基于FPGA的GPS相关器改进方案

摘 要:在GPS芯片或者其他信号处理芯片中,经常需要做移动相位进行相关的运算,用硬件来实现这样的运算是相当耗资源的,但有时候也不可避免。基于此,在传统的采取循环移位寄存器存储数据并且移位来进行相关运算的基础上提出一种新的方案,考虑到FPGA有大量现成的Block RAM可以利用,所以采用Block RAM来存储数据并且通过改变Block RAM地址来进行相关运算,理论和实践证明,该方法达到了同样的目的并且更加经济有效,节省了大量资源。

关键词:循环移位寄存器;FPGA;Block RAM;GPS

中图分类号:TP368.1文献标识码:B

文章编号:1004-373X(2008)22-175-03

Improved Scheme of GPS Correlator Based on FPGA

ZHANG Dan,ZHAO Yong

(School of Computer& Information Engineering,Shenzhen Graduate School,Peking University,Shenzhen,518055,China)

Abstract:In the GPS chip or other signal processing chips,some mobility of phase to correlate operation,sometimes,it is quite wasteful and inevitable to use the hardware realize the operation.A new scheme based on the traditional idea which uses the cycle shift registers to store data and shift the phase to do correlate operation.Considering the abundant free Block RAM in FPGA,the Block RAM is used to store our data and change the address of the Block RAM to do some correlate operation.Theory and experiment prove that this method is right and more economic and proficient,as well as saving abundant resource.

Keywords:cycle shift registers;FPGA;Block RAM;GPS

随着美国联邦通信委员会所制定的E911(Enhanced 911)安全条款,规定在2005年年底之前,所有新推出的手机都需配备简易的定位功能,以方便救助单位及时找到通话者的位置,日本政府2004年宣布,将GPS接受功能列为3G手机的基本规格,并表示2007年4月后上市的手机,均配备GPS接收功能,尽管现在集成GPS功能的手机还没进入主流市场,但是将来的3G手机的中高端机型会普遍集成GPS功能[1]。伴随着这样一种时代背景,GPS接收机芯片产业如雨后春笋般呈现出一种蓬勃发展的局面。

在高动态的GPS接收机中,为了跟踪和解码GPS信号,首先要在短时间内快速捕获到GPS信号,将捕获到的GPS信号传递给跟踪过程,再通过跟踪过程解调便可得到卫星的导航电文,所以怎样快速捕获到卫星信号是GPS接收机的一个最重要的问题之一。而在这个过程中,相关器部分占据了非常重要的位置,是最耗资源最耗时间的部分,一般GPS接收机具有多个相关通道[2],每个相关通道主要由载波锁定环路和C/A码延时锁定环路组成,载波锁定环路用来跟踪卫星信号载波频率和载波相位,达到载波同步,C/A码延时锁定环路用来使本地码相位与接收机的GPS卫星信号中的C/A码相位保持同相,以实现对卫星信号的解扩和伪距离测量[3]。本文研究的重点就是C/A码延时锁定环路中的数据存储问题。

传统的GPS的基带处理芯片中的相关器[4],是在不同频点,通过移动本地码相位与卫星信号进行相关计算。当在该频点在每个码相位都进行了相关计算之后,再改变频点重复做这样的相关运算,本文从节省FPGA资源方面考虑,对该模块进行了改进。

1 循环移位寄存器存储、移相方案

GPS发送的卫星信号包括了载波、导航电文、伪随机码(C/A码和P码)[5],其中C/A码作为民用伪随机码是本文研究的对象,它的周期为1 ms,在1 ms内有1 023个码片。因为C/A码的是基于GOLD序列产生的,所以C/A码在每个周期有1 023种序列,由于1 023不是基2或者基4的数据,并不利于分块复用处理,故需要对本地C/A码以及输入数据进行补“0”操作,构成1 024位[6]。

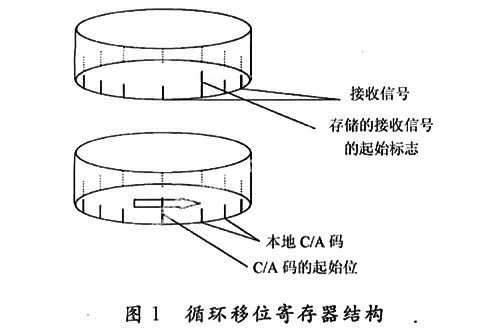

因为希望更加精确地捕获和跟踪卫星信号,对本地C/A码进行4倍采样,扩展到4 096位,传统的本地生成的C/A码是一种循环移位寄存器的存储方式,即每次移动完1个码片,计算完相关数据之后,4 096个码片就向左移动一个码片,最高位补到最低位。直到完成了所有移位,其基本结构如图1所示[7,8]。

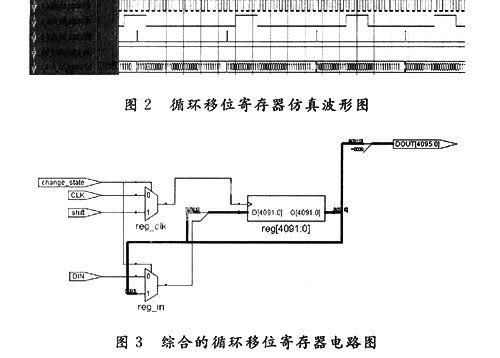

这种方法的优点是结构简单易懂,设计也相应很简单,但是非常消耗FPGA资源,根据这种方法得到的仿真波形图和综合电路图如图2和图3所示。

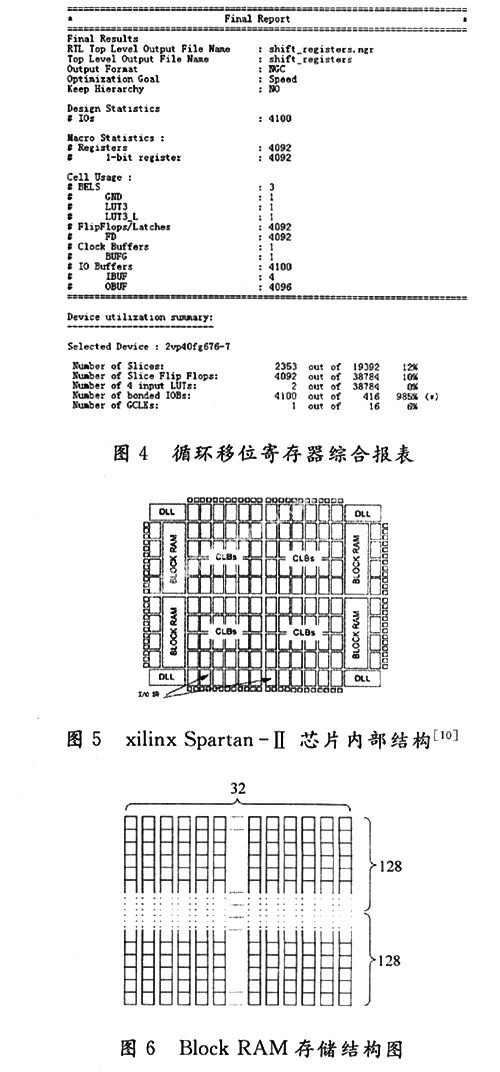

根据循环移位寄存器存储、移相方案,用XILINX ISE综合得到的Resource Usage Report如图4所示。该模块的接口超出了FPGA资源,但和其他模块连接的时候就不会有这样的问题,所以可以不用考虑。由该报表可以看出此种方案没有消耗FPGA的Block RAM资源,但是消耗的Slices资源有2 353个之多。

2 Block RAM存储、变址方案

根据采用循环移位寄存器存储数据并且移位来进行相关运算的方案综合后的结果可以看到,这种方法需要移动4 096次码相位,消耗的资源相当大,但XILINX FPGA器件提供的片内的RAM可直接使用,而不必使用寄存器来构成存储空间,从而大大提高了FPGA的利用率。在XILINX FPGA产品中[9],根据型号的不同,提供2种RAM 结构: 分布式RAM和Block RAM。

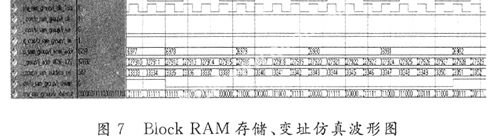

如图5所示Block RAM存储器按列排列,左边从0列开始,每隔12 列CLB 排列1个Block RAM存储器。每个Block RAM是一个完全同步的双端口RAM,每个端口都有独立的控制信号, 本文正是采用了FPGA现成资源Block RAM实现,用32个宽度为1深度为256的RAM完成。其中前32×128个数和后32×128个数是一样的,即后面32×128的对前面数据的复制,这种方法不需要再移动数据,而是采取改变地址的方式进行。同样也需要改变4 096次地址,其结构框图如图6所示。

Block RAM写入逻辑的写地址用13位二进制数表示,其中高8位选定行(256行),低5位选定列(32列),这个过程需要对计数器进行译码产生32个列选择使能信号,使数据从左到右依次导入到RAM中。

Block RAM读出逻辑:刚开始从第1列第1行开始按照蛇行顺序读取数据,即第1次读出的4 096个数据是从第1行第1列数据到第128行第32列数据,进行完1次相关运算;第二次读出的4 096个数据是从第2行第1列数据到第129行第1列数据,再进行1次相关运算,第三次读出的4 096个数据是从第3行第1列数据到第129行第2列数据,完成1次相关运算…这样依次进行下去,每进行完1次相关计算后,改变1次行地址和列地址再进行下次相关计算,直到改变4 096次地址结束该点频率的所有相位相关计算,得出峰值最大点的码相位。

根据以上讨论,采取Block RAM存储、变址方案,同样可以实现移动本地C/A码4 096个码相位与接收到的卫星信号进行相关计算。用Modelsim仿真的结果如图7所示。

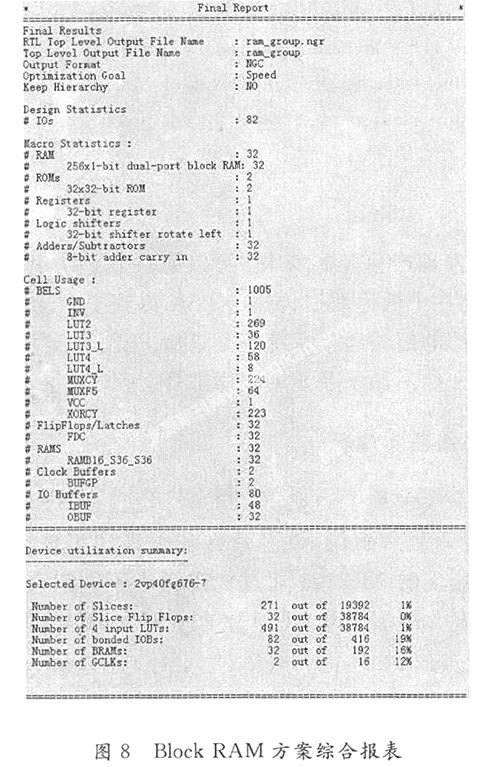

根据采取的FPGA提供的Block RAM来存储数据、改变地址达到循环移位的方案,用XILINX ISE综合后得到的Resource Usage Report如图8所示。

对比2种不同方案得到的综合报表,可以看到,第一种方案即采用循环移位寄存器来存储数据并且移位来进行相关运算的方案没有消耗FPGA的Block RAM资源,但是消耗的Slices资源有2353。而第二种方案采取FPGA现有的Block RAM存储、变址方案,消耗了32个Block RAM,但消耗的Slices资源只有271个,比第一种方案节约了将近90%的资源。

3 结 语

虽然两种方法都实现了我们的目的,但是对比两种方案的综合报告,可以看出,基于循环寄存器移位方案在综合后用掉了XILINX FPGA器件大量的Slices资源,而充分考虑FPGA器件结构,选择资源占用最少、效率最高的实现方法,用其自带的存储器Block RAM设计,则仅用相当少的Slices资源。明显后一种设计可以充分节省现有的FPGA资源,设计出容量更大的存储器,且更经济、有效。 所以理论和实践都证明,该方法可行。该方法同样适用于其他相关运算的芯片设计。

参考文献

[1]巴晓辉,李金海,陈杰.世界主流GPS芯片介绍[J].今日电子,2007(3):44-48.

[2]薛雅娟.GPS接收机数字基带信号处理算法研究[D].成都:成都理工大学,2007.

[3]干国强,邱致和.导航与定位[M].北京:国防工业出版社,2001.

[4]Elliott D Kaplan,Christopher J Hegarty.Unders tanding GPS Principles and Application[M].Second Edition.2007.

[5]Jeremy Allnutt.Satellite Communications[M].Second Edition.2005.

[6]魏敬法.GPS信号快速捕获的FPGA实现[D].北京:中国科学院研究生院,2005.

[7]储钟圻.数字卫星通信[M].北京:机械工业出版社,2006.

[8]罗宇平.GPS信号的快速捕获与跟踪方案的研究[J].电子信息工程,2007.

[9]佚名.FPGA平台架构用于复杂嵌入式系统.http://www.eeworld.com.cn/designarticles/embed/200712/17144.html.

[10]佚名.基于查找表结构(LUT)的FPGA结构.http://www.fpga.com.cn/advance/structures/lut.htm.

[11]刘华珠,陈雪芳,黄海云.基于FPGA技术的DRAM分时存取方法.现代电子技术,2005,28(10):111-112,115.

作者简介 张 丹 男,1980年出生,四川仁寿人,北京大学深圳研究生院信息工程学院硕士研究生。主要研究方向为数字ASIC,FPGA。

赵 勇 男,加拿大Concordia University电气工程系博士后,北京大学信息科学技术学院副教授。主要从事视频压缩以及移动视频终端、基于CDMA的视频传输系统,以及智能手机的研究开发工作。