基于SEP5010芯片的引导方案的研究与优化

摘 要:系统引导是嵌入式系统开发过程中的一个重要环节,其启动速度是嵌入式系统一个重要指标。对东南大学自主研发的SEP5010芯片的引导方案的研究,正是从提高启动速度,缩短启动时间方面来考虑的。从配置最优分频比、打开缓存(I-cache)、选择下载协议、设计不同功能的启动方式这4个方面对引导方案进行研究与优化。实验表明,通过以上优化,系统启动时间大大缩短,启动速度平均要提高84.7%,满足了嵌入式系统对快速启动的要求。目前,该引导方案已经成功应用于一款手持导航设备。

关键词:系统引导;SEP5010;缓存;XMODEM

中图分类号:TP302.1文献标识码:B

文章编号:1004373X(2008)2200103

Research and Optimization of Booting Scheme Based on SEP5010 Chip

BAO Dan,SHI Jianlong,QI Longning,HU Chen

(National ASIC System Engineering Research Center,Southeast University,Nanjing,210096,China)

Abstract:System booting is an important aspect in real-time embedded system,of which booting speed is one of the most important indexes.As to the realization and optimization methods of the system booting scheme based on SEP5010 chip independently developed by Southeast University,this research mainly considers how to increase the booting speed and shorten the booting time.Through the research of configuring optimal frequency division ratio,opening I-cache,selecting downloading protocol and designing several booting schemes with different functions,the booting performance can be obviously increased.the optimization described above in the experiment which on real platform could improve the average booting time by 84.7%,which satisfies the demand of fast booting in embedded system.Presently,the booting scheme has been applied to a handheld navigation device.

Keywords:boot;SEP5010;cache;XMODEM

1 引 言

在嵌入式系统开发过程中的一个重要问题是如何开发系统启动代码,它是硬件和软件的枢纽。对于嵌入式系统,启动代码是基于特定硬件平台来实现的。不同的处理器架构都有不同的启动代码,它不但依赖于CPU 的体系结构,而且依赖于嵌入式系统板级设备的配置。 对于不同的嵌入式板而言,即使它们使用同一种处理器,启动代码也是不同的。由于启动代码的实现依赖于 CPU 的体系结构,因此大多数启动代码都分为 stage1 和 stage2 两大部分。依赖于 CPU 体系结构的代码,比如设备初始化代码等,通常都放在 stage1 中,而且通常都用汇编语言实现,以达到短小精悍的目的。而 stage2 则通常用C语言来实现,这样可以实现更复杂的功能,而且代码会具有更好的可读性和可移植性。本文实现并优化的是基于东南大学自主研发的SEP5010芯片的stage1部分的启动代码,通过配置最优分频比,打开缓存(I-cache),选择下载协议和设计不同功能的启动方式这4个方面来对它进行优化,缩短启动时间,提高启动速度,为下一阶段镜像的加载和执行做好准备。

2 硬件平台与软件平台介绍

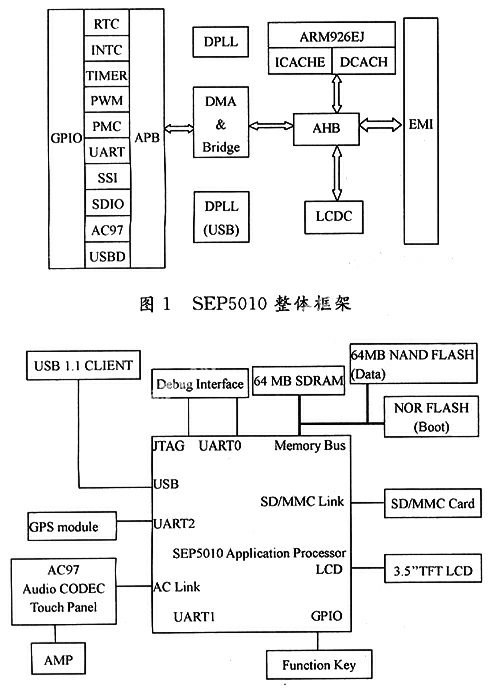

嵌入式系统是整个系统的核心,包括硬件平台和软件平台。本文采用东南大学自主研发的SEP5010芯片,整体框架如图1所示,其最高主频达300 MHz,扩展了64 MB的SDRAM,2 M×32 b的Nor FLASH和64 M× 8 b的NAND FLASH,外围资源丰富。本文所采用的开发平台为基于SEP5010芯片的手持导航系统平台,面向低成本手持设备,本开发平台的系统框图如图2所示。

平台软件采用WinCE 5.0作为系统的操作系统,它是一个功能强大的实时嵌入式操作系统。可通过本文设计的启动方案引导EBOOT程序,最终由EBOOT引导WinCE内核。

3 启动方案详细介绍

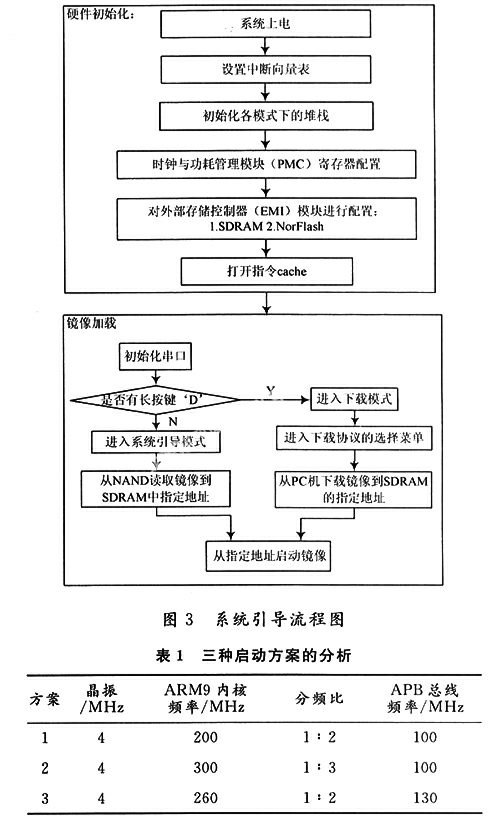

如图3所示,系统从外部Nor FLASH存储器启动。首先,对SEP5010芯片的时钟与功耗管理模块(PMC)进行相应的配置。选择内核频率,配置总线与内核的分频比,最后得到APB总线频率。然后,对SEP5010芯片的外部存储控制器(EMI)模块进行配置,根据本开发板上所使用的SDRAM芯片型号(本开发板所使用的SDRAM型号为:W982516BH75L。其工作频率小于133 MHz,行地址为13 b,列地址为9 b)配置其行列地址和时序参数, 并且选通Nor FLASH。最后打开I-cache并跳转到Main()主函数去执行。进入Main() 函数后,首先初始化串口,配置波特率为115 200 b/s,配置接受和发送的数据结构为:8个数据位,1个停止位,无奇偶校验。其次初始化NAND FLASH,配置NAND FLASH芯片的时序(本开发板所使用的NAND型号为:K9F1208UOB,时序配置采用芯片手册上的默认配置)。然后通过检测有无长按键进入不同的功能模块:检测到没有长按键,进入直接引导模式,从NAND FLASH直接读取镜像到SDRAM中指定地址去执行,反之,若检查到有长按键,进入更新模式,通过菜单项选择下载协议:标准XMODEM或1 k-XMODEM,下载镜像到SDRAM中指定地址去执行。最后从指定地址启动镜像。

4 启动方案的性能优化设计与分析

4.1 配置最优的时钟分频比,提高代码执行速度,加快启动速度

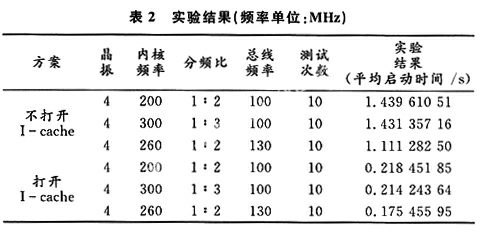

本文采用的SEP5010芯片,内部集成ARM公司的ARM926EJ-S微处理器,它的最高主频达到300 MHz。外部扩展了64 MB的SDRAM,其最高工作频率为133 MHz。要想系统运行和处理速度达到最快,就必须使得主频和总线频率尽可能高,同时又要保证其运行性能的稳定。因此,就需要选择合适的内核频率,配置最优的时钟分频比来达到最优组合。由于分频比寄存器只支持不分频,2分频,3分频和4分频4种分频方式,因此分析3种方案如表1所示。

分析比较方案1和方案2,在SDRAM频率不变的前提下,将主频提高(此时主频提高了1.5倍,已经到达其300 MHz的极限值)一定会使运行速度提高,故方案2优于方案1。

分析比较方案2和方案3,将SDRAM频率提高到1.3倍,主频降低到0.87倍,这时内存频率得到了较大幅度的提高(此时SDRAM的频率几乎已经达到133 MHz的极限值),而内核频率的降低幅度很小,故方案3的启动速度一定会优于方案2。

4.2 打开I-cache,提高程序的运行速度,加快启动速度

I-cache功能一般是在MMU开启之后被使用的(为了降低MMU查表带来的开销),但并不是说MMU被开启了I-cache才能被开启,本启动方案只是最简单的硬件初始化,并不需要打开MMU,但是却可以打开I-cache来加快启动速度。

由于本方案从NOR启动,本平台采用的NOR芯片为16 b,而内核为32 b,故CPU每次需从NOR读取2次,才能完整读取1条指令;而NOR的1个读周期为70 ns,这样如果直接从NOR读取1条指令需要140 ns,CPU大量的时间都在等待,极大的降低了启动速度。打开 I-cache后,CPU可以直接在I-cache中执行指令,并直接从I-cache中返回,不需要从NOR中读取,加快了执行速度。

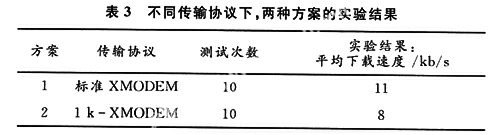

4.3 通过传输协议的优化来加快镜像下载速度

本方案的镜像下载方式为串口下载,协议为XMODEM协议。XMODEM协议是一种异步文件运输协议。标准XMODEM协议以128字节块的形式传输数据,并且每个块都使用1个校验和过程来进行错误检测。如果接收方关于1个块的校验和与它在发送方的校验和相同时,接收方就向发送方发送1个认可字节(ACK),否则发送NAK。而1 k-XMODEM它以1 024 B一块来传输数据,提高了传输速率,同时增加了 CRC 校验,用来提高传输的可靠性。由此可见,采用1 k-XMODEM协议,每次传输的数据更多,可以加快镜像的下载速度。

4.4 通过设计不同的启动方案,满足不同用户的需求

方案一 当系统启动后,通过串口打印的菜单项选择进入不同的模块。选择1为进入下载更新模块,通过串口下载和更新镜像;选择2或者在设定的时间范围(3 s)无按键,则进入直接引导模块,从NAND FLASH中引导已存在的镜像。

方案二 当系统启动后,通过是否有长按键的检测,进入不同的功能模块,即有长按键,进入更新模块,通过串口,下载和更新镜像;反之,没有长按键,则进入直接引导模块,从NAND FLASH中引导已存在的镜像。

采用方案2的设计可以使得芯片的开发者与最终用户的需求分开,既满足了开发者调试的功能,又实现了最终用户直接启动的功能。故采用第二种方案。

5 实验结果

(1) 在是否打开I-cache 情况下,分别配置不同的时钟分频比,比较和分析系统启动时间,其实验结果如表2所示:

本实验采用不按长按键,直接从NAND读取镜像并运行的启动方案来测量和比较不同方案的启动时间的长短。其中烧写到NAND中的镜像为56.8 kB大小的eboot镜像。系统启动时间的计算方法为:通过利用本芯片中的Timer模块的计时器功能,对启动程序进行计时,时间为从进入主函数开始,直到从NAND读取完镜像并开始运行为止。

实验结果证明,采用1∶2的分频比,打开I-cache,并且将主频设成260 MHz,APB总线频率达到130 MHz的情况下,启动时间最短。另外由实验结果可见在相同频率及分频比配置的前提下,打开I-cache后的启动时间比未打开I-cache的设计平均提高84.7%。由此可见尽可能地提高存储总线频率优于单纯提高内核频率的设计。

(2) 通过选择不同的传输协议,比较和分析两种方案的实验结果如表3所示:

实验结果证明选择1 k-XMODEM下载镜像的速度更快。

6 结 语

通过以上实验结果可知,通过配置适当的内核频率,选择最优的时钟分频比,并且打开I-cache可提高系统引导速度,缩短启动时间;通过选择1 k-XMODEM的传输协议可加快镜像下载速度。另外,通过长按键的设计,使得芯片的开发者与最终用户的需求分开,既满足了开发者调试的功能,又实现了直接启动的功能,缩短了启动时间。通过以上4方面的优化,系统启动时间大大缩短,满足了嵌入式系统快速启动的要求。目前,该启动方案已经应用于一款手持导航设备的开发中,并且对相关的嵌入式系统开发也具有一定的参考意义。

参 考 文 献

[1]国家专用集成电路工程技术研究中心.SEP5010用户手册\.2004.

[2]张冬泉.Windows CE实用开发技术\.北京:电子工业出版社,2006.

[3]时龙兴.嵌入式系统基于SEP3203微处理器的应用开发\.北京:电子工业出版社,2006.

[4]齐欣,张家栋,霍凯.ARM核微处理器Bootloader的分析与应用\.现代电子技术,2006,29(11):2-4.

[5]王建,许毅平,周曼丽.ARM7嵌入式系统中Bootloader分析与设计\.微计算机信息,2006,22(5):134-136.

[6]张建义,袁嫣红,齐玲玲.ARM9启动机制分析\.浙江理工大学学报,2007,24(2):2-3.

[7]张宏财,赵曾贻.基于ARM核的Bootloader代码的分析与设计\.微计算机信息,2006,22(2):1-3.

[8]白浪,张思东.WinCE系统下BootLoader的开发\.单片机及嵌入式系统,2004(2):2-4.

[9]黄克彬,叶梧,冯穗力.基于ARM嵌入式开发的调试方案\.计算机工程,2004,30(24):2-3.

[10]George M R,Wong W F.Windows CE for a Reconfigurable System-on-a-Chip Processor Field-Programmable Technology\.IEEE International Conference,2004:201-207.

[11]刘娅.基于ARM嵌入式系统的Bootloader的设计与实现\.现代电子技术,2006,29(7):142-144.

作者简介 鲍 丹 女,1981年出生,东南大学集成电路学院软件工程专业工程硕士研究生。研究方向为嵌入式系统。

时建龙 男,1981年出生,东南大学集成电路学院软件工程专业工程硕士研究生。研究方向为嵌入式系统设计。

戚隆宁 男,1979年出生,东南大学国家专用集成电路系统工程技术研究中心博士研究生。研究方向为嵌入式系统低功耗技术。

胡 晨 男,1967年出生,东南大学电子工程系教授。