Gbps试验系统中高速串行接口的设计与实现

摘 要:介绍Gbps无线通信试验系统中高速串行数据接口的设计与实现。按照Gbps无线通信试验系统对高速串行数据的传输要求,数据传输速率超过1 Gb/s,在基于Xilinx IP core技术上对单板上的FPGA进行逻辑设计,实现了符合系统要求的高速串行数据接口。在系统实际调试中,通过ATCA机箱背板进行数据传输,获得了高达Gbps的数据吞吐速率且传输误码率低于10-14。

关键词:Gbps;高速串行接口;FPGA;ATCA

中图分类号:TP336文献标识码:B

文章编号:1004373X(2008)2200404

Design and Implementation of High Speed Serial I/O Interface in Gbps Experimental System

WANG Xiangyang,ZHAO Yanjie

(National Mobile Communications Research Laboratory,Southeast University,Nanjing,210096,China)

Abstract:The design and implementation of high speed serial I/O interface in the Gbps wireless communication experimental system is presented in this paper.In accordance with requirements of high speed serial data transmission in the Gbps wireless communication experimental system,the data transmission rate surpasses 1 Gb/s.The high speed serial data interface module is implemented by carrying on logic design in FPGAs of single boards based on Xilinx IP core.According to actual system debugging,the data throughput up to Gbps is achieved by data transmission through ATCA chassis with full-mesh backplane.The bit error rate is below 10-14。

Keywords:Gbps;high speed serial interface;FPGA;ATCA

1 引 言

目前,互连网的普及推动了视频会议、网络电视以及远程教学等许多宽带业务的应用,也促进了高速网络不断向前演进。在系统级互连接口中,高速串行I/O技术由于其高性能和简化设计的优点,正在迅速取代传统的并行I/O总线技术而成为业界趋势。本文讨论国家863课题“Gbps无线传输关键技术与试验系统研究开发”项目中的高速串行接口模块设计。

试验系统主要基于Xilinx公司最新推出的Virtex-5(V5)系列FPGA[1]。V5系列采用65-nm铜线CMOS工艺和低功耗的IP模块,共包括LX,LXT,SXT和FXT四款平台。其中,LXT和SXT两款平台中内嵌了三模式以太网MAC(Media Access Control)模块和RocketIO GTP 收发器模块[2]。

V5嵌入式三模式以太网MAC为多种网络接口提供经济便利的解决方案,能够以10/100/1 000 Mb/s的速率连接BASE-X和BASE-T网络。它和V5 RocketIO GTP 收发器相结合,能够让用户与各种网络设备进行连接。千兆以太网MAC和RocketIO GTP收发器的集成可以简化物理层与数据链路层之间的通信连接。Gbps试验系统中的高速串行接口就是基于此集成设计实现的。

2 嵌入式三模式以太网简介

V5嵌入式三模式以太网MAC是FPGA内嵌的一个硬核,它完全符合IEEE Std 802.3规范[2],在V5系列芯片中,每个嵌入式以太网MAC模块包含2个独立的以太网MAC(EMAC0和EMAC1),其主要特性有[3,4]:

(1) 支持10/100/1 000 Mb/s三种模式以太网MAC业务;

(2) 可配置的全双工(10/100/1 000 Mb/s)和半双工工作模式(10/100 Mb/s);

(3) 支持FCS(Frame Check Sequence);

(4) 硬件可选择的DCR(Device Control Register)总线接口或通用主机总线接口;

(5) 可配置的流量控制功能。

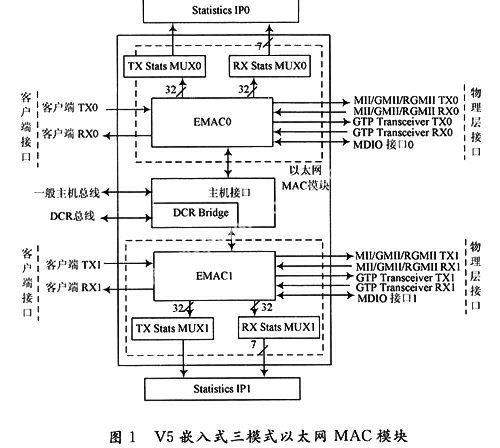

图1为V5嵌入式三模式以太网MAC模块结构框图。

每个以太网MAC模块都有独立的发送端和接收端,提供全双工通信。通用主机总线或DCR总线用于访问主机接口,通过主机接口可以访问以太网MAC的配置寄存器(巨帧使能、暂停、单播地址以及帧校验序列生成)。每个以太网MAC的物理层接口可以配置成MII/GMII,RGMII/SGMII或1000BASE-X接口,并且都有1个可选择的MDIO接口[1],通过它可以访问外部物理层管理寄存器或以太网MAC中PCS/PMA模块内置的物理层接口管理寄存器。

当以太网MAC配置成1000BASE-X PCS/PMA模式时,PCS/PMA模块与RocketIO收发器联合工作,能够提供与IEEE 802.3系列标准[2]定义的千兆比特同轴或光纤收发器直接连接所需要的全部功能。这可以避免1000BASE-X网络应用所需的外部物理层芯片。

3 RocketIO GTP收发器简介

V5 RocketIO GTP收发器是FPGA内嵌的1个硬核,具有通用性和低功耗等特性,支持多种标准协议,如Aurora,Serial RapidIO,Gigabit Ethernet(GE)等[5]。

V5 RocketIO GTP收发器主要特性包括:

(1) CML(Current Mode Logic)串行驱动/具有可配置终端的缓冲器;

(2) 可编程的发端预加重技术和收端均衡技术用于保持信号完整性;

(3) 支持100 Mb/s到3.2 Gb/s的传输速率;

(4) 支持内部PCS的多种特性:8 B/10 B编解码,时钟校正和信道绑定等;

(5) OOB(Out of Band)信号,包括支持PCI Express和SATA标准的COM信号。

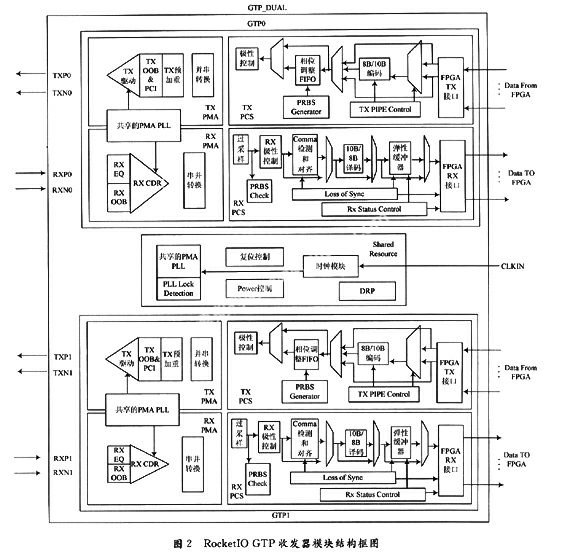

在V5 LXT和SXT器件中,每个GTP-DUAL模块包含2个GTP(GTP0和GTP1),图2为GTP-DUAL的模块结构框图。

其中,2个GTP模块共享1个PLL(Phase Locked Loop),从而减少FPGA芯片面积及降低功耗。每个GTP模块包括1个独立的发送模块和接收模块。发送模块和接收模块均由PCS(Physical Coding Sublayer)和PMA(Physical Media Attachment)构成。PMA是收发器的数/模混合部分,主要包括串/并和并/串转换、共享PMA PLL模块、接收时钟恢复电路以及发端预加重和收端均衡模块。PCS子层是收发器的数字部分,主要包括8 B/10 B编解码模块、极性控制模块、伪随机序列生成模块以及相位调整FIFO模块和过采样模块。在数据传输过程中,发送端将上层客户端的数据(8/16 b)通过PCS和PMA子层处理后通过传输物理介质以串行方式发送出去。接收端将物理介质上传送过来的数据通过相反的操作送到上层客户端。

4 Gbps试验系统中的高速串行接口设计

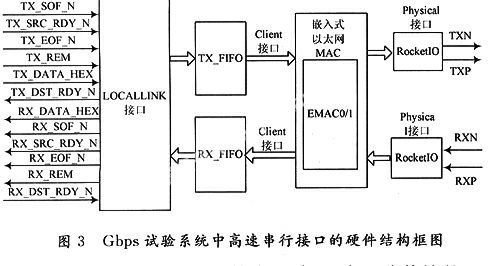

在试验系统中FPGA间接口要求高达数Gbps量级的数据吞吐率。为简化逻辑设计,系统中基于Xilinx公司的嵌入式三模式以太网MAC IP Core来实现数据链路层和物理层协议。该IP Core可以将支持1 000 Mb/s的MAC协议与Rocket IO GTP收发器集成在一起,从而实现Gbps的数据传输速率。图3为Gbps试验系统中高速串行接口的实现结构框图。

如图3所示,接口缓存TX_FIFO模块和RX_FIFO模块主要完成存储转发功能,并可进行异步时钟域的转换。对于发送数据,模块TX_FIFO首先以Locallink接口[1]时序接收用户侧的发送数据,将其写入内部缓冲区中,再将此数据读出送往底层IP Core封装的以太网MAC用户端接口,最后通过RocketIO串行接口以差分信号发送;对于接收数据,底层封装的IP Core将接收数据存储到RX_FIFO模块的内部缓冲区中,再按照Locallink接口时序送到用户侧。因此,上层用户侧实际对应一个标准Locallink接口进行操作。

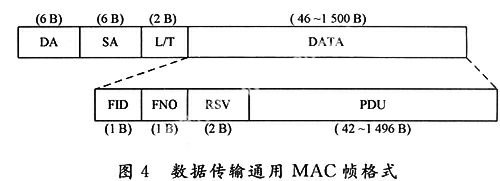

在本系统中传输的所有数据包都遵照IEEE 802.3标准定义的MAC帧格式[6,7]。图4为系统中传输数据的通用MAC帧格式。

如图4所示,DA域是MAC帧格式中6 B长度目的地址,SA域是6 B长度的源地址,L/T域是MAC帧的字节长度或者控制帧的类型信息。DATA域是MAC帧格式的数据段。因为系统中多种不同数据类型的传输需要进行不同的处理,所以在承载的上层用户数据前添加了长度4 B的控制域信息组成一个标准MAC帧进行传输。

分别定义如下:

FID: 1个字节的数据帧类型域,用来区分传输的不同用户数据类型;

FNO:1个字节的数据帧序号域;

RSV:2个字节的保留域,用作系统扩展定义。

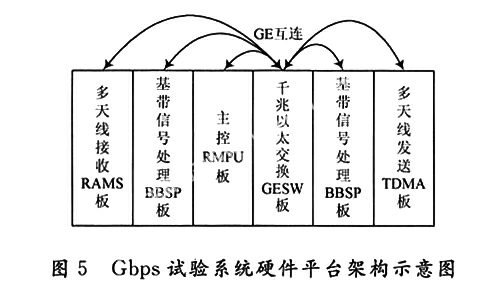

试验系统中的基带硬件平台采用符合PICMG3.0工业标准的14槽位全连接背板架构的ATCA(Advanced Telecommunication and Computing Architecture)机框[8]。

在ATCA机箱内采用1块符合标准GE协议的千兆以太交换GESW板,系统中任意两块功能单板的数据可以经背板通过GESW板实现全双工传送。试验系统包括主控RMPU板,多天线接收RAMS板,多天线发送板TDMA板和基带信号处理板BBSP板等不同功能单板,如图5所示。

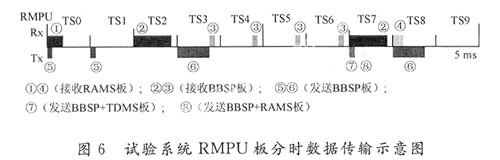

为了防止发生拥塞,根据不同功能单板的数据传输需求,试验系统中各单板间的数据采用分时工作模式,即在不同的时间片内通过GESW板交换传输两块功能单板之间的数据流量,通过实际数据吞吐率的计算分配时间片,降低系统的流量控制复杂度。

以主控RMPU板为例[9],图6所示为RMPU板在系统帧定时中不同时隙与各功能单板交互传输不同数据类型。由图可见,在TS0和TS8时隙,RMPU板分别接收RAMS板发送来的类型1和4数据,在TS8时隙RMPU板同时向RAMS板和BBSP板发送类型8数据。

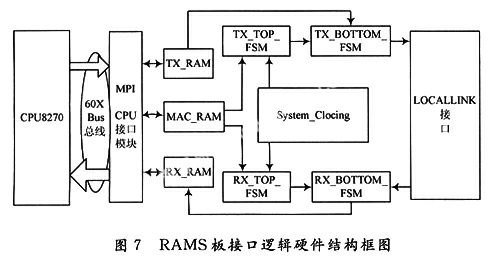

通过合理设置,GESW板可以透明传输系统任意两块功能单板间的GE帧格式数据包。仅通过高层控制模块对不同单板的MAC参数配置,本文在FPGA中实现的底层接口逻辑可以通用于各功能单板之间的高速串行数据传输接口。以下通过RAMS板上接口逻辑为例,介绍RAMS板与RMPU板之间的高速串行数据传输的设计与实现。图7示意了RAMS板底层接口逻辑的实现结构框图。

首先,RAMS板CPU通过60x Bus总线将MAC层组帧所需要的DA、SA和L/T域等参数写入存储器MAC_RAM,需要发送的用户数据预先置入缓冲区TX_RAM。发送数据时,从MAC_RAM里读出需要的控制信息,并从TX_ RAM里读出发送的用户数据,组合成符合IEEE 802.3标准定义的MAC帧格式数据包,在顶层和底层发送状态机的控制下送往底层LocalLink接口。接收数据时,接收状态机控制从MAC_RAM里读出需要接收的MAC地址与收到的数据包中目的地址域进行比较,如果匹配则接收并存储负载数据到接收数据缓冲区RX_RAM,如果不匹配则丢弃该数据包。另外,还可以通过匹配承载的数据帧类型和数据帧序号等参数进一步完成对接收数据帧的校验和滤除。

RMPU板实现的串行传输接口逻辑结构及功能和RAMS类似,但是两者的系统定时模块配置不同,以实现试验系统中功能单板的分时传输工作模式。

5 结 语

本文介绍Gbps试验系统中高速串行接口的设计与实现。该接口是基于Xilinx FPGA的嵌入式GE MAC和RocketIO GTP收发器来实现,这在很大程度上简化了物理层和数据链路层之间的通信连接。通过RMPU板与RAMS板的接口设计为例,本文介绍试验系统中各单板之间的高速串行数据传输方案。通过灵活配置底层通用逻辑,本文讨论的设计实现了各功能单板间高达Gbps的高速串行数据传输。试验系统的硬件调试结果表明,系统的高速串行数据传输误码率低于10-14。

参 考 文 献

[1]http://www.xilinx.com.

[2]Virtex-5 Family Overview LX,LXT,and SXT Platforms.DS100 (v3.1),2007.

[3]Virtex-5 Embedded Tri-Mode Ethernet MAC User Guide.UG194(v1.2),2007.

[4]Virtex-5 Embedded Tri-Mode Ethernet MAC Wrapper v1.3.UG340,2007.

[5]Virtex-5 RocketIO GTP Transceiver User Guide.UG196(v1.3),2007.

[6]IEEE Std 802.3-2002 Part3:Carrier Sense Multiple Access with Collision Detection (CSMA/CD)Access Method and Physical Layer Specification IEEE,Computer Society.

[7]佚名.TCP/IP详解卷1:协议\.北京:机械工业出版社,2000.

[8]PICMG 3.0 Advanced Telecommunications Computing Architecture (ATCA) Version D1.0.

[9]王向阳.B3G ATCA 平台GE传输方案概要设计\.2008.

[10]夏宇闻.Verilog 数字系统设计教程\.北京:北京航空航天大学出版社,2003.

作者简介 王向阳 东南大学移动通信国家重点实验室硕士生导师,副教授。

赵艳杰 东南大学移动通信国家重点实验室硕士研究生。